(2)

# A 0.18µm Low Power, High Speed Ternary Content Addressable Memory

Ankaj Gupta\*, AnkitGambhir

Department of Electronics Engineering, Delhi Technical Campus, Greater Noida (UP), India

#### Abstract Article Info Ternary content addressable memory or associative memory have their primary application in Article history: today's Network Router In all web hased search engine TCAM Received 25 January 2017 memory is employed. But power consumption is a major issue with a TCAM. In this paper a Received in revised form lowpower ternary content addressable having very low leakage is proposed. Simulation 20 February 2017 results shows upto 30% reduction in power. The circuit has been deesigned and implemented Accepted 28 February 2017 in 0.18 µm CMOS technology. The circuit dissipated a maximum 10.5 nW of power and is Available online 15 March 2017 suitable for low power application. Keywords Power dissipation. leakage. speed. TCAM

### 1. Introduction

An efficient hardware solution to perform table lookup is the ternary content addressable memory (TCAM). TCAM searches for matching data by content and returns the address at which the matching data is found. TCAMs are used extensively today in applications such as network address translation, pattern recognition, and data compression. In these applications, there is a steady demand for TCAMs with higher density and higher search speed, but at constant power. Currently, commercial TCAMs are limited to 18 Mb of storage and 100 million searches per second on a 144-bit search word, at typically 5 W per TCAM chip. Compared to the conventional memories of similar size, TCAMs consume considerably larger power. This is partly due to the fully parallel nature of the search operation, in which a search word is compared in parallel against every stored word in the entire TCAM array.

A TCAM can be used as a co-processor for the network processing unit (NPU) to offload the table lookup tasks. Besides the networking equipment, TCAMs are also attractive for other key applications such as translation look-aside buffers (TLBs) in virtual memory systems [1-2], tag directories in associative cache memories [3-4], database accelerators [5], data compression [6], and image processing [7]. Recent applications of TCAMs include real-time pattern matching in virus/intrusion-detection systems and gene pattern. searching in bioinformatics [8-9]. Since the capacities and word-sizes of TCAMs used in most of these applications are much smaller than the TCAMs used in networking equipment, the current TCAM research is primarily driven by the networking applications, which require high capacity TCAMs with low-power and highspeed operation.

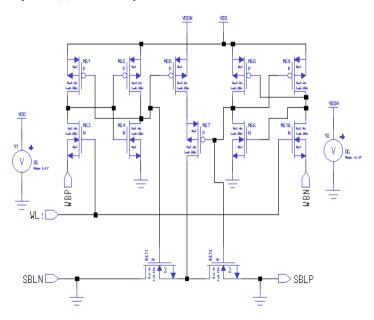

# 2. Proposed low Power High Speed Cell

The proposed low power circuit has shown in Fig. 1. This TCAM cell use two independent cell for storing '1', '0' and 'X'. 'X' is mask state. The crcuit uses AND type match line. Transistor 11 and 12 store complementary valuewhen store word is either 0 or 1. Transistor 5 and 7 are used to charge node between search line. Transistor 11 and 12 perform the comparaision operation i.e. XOR operation.

The static power of CMOS circuit is given y equation (1)

$$P_{S}=I_{L} * V_{DD}$$

(1)

Where.

IL= Leakage current of the circuit

The subthreshold leakage current of NMOS transistor with zero  $V_{GS}$  voltage and full swing  $V_{DS}$  is given by equation (2) [9].

Corresponding Author,

E-mailaddress:ankajgarg87@gmail.com Phone No--+91-9992249116 All rights reserved: http://www.ijari.org

$$I_{SV} = I_o \exp\left(-\frac{K_1\sqrt{\phi_s} - K_2\phi_s - \eta V_{dd}}{nV_r}\right)$$

Where,

$$I_o = \mu_o C_{ox}(\frac{We_{ff}}{Le_{ff}}) Vr^2 e^{1.8}$$

$\eta = barrier \ lowering \ parameter$

$K_1$ ,  $K_2$  = no uniform doping effect parameer

$V_T$  = thermal voltage = KT/q

$\mu_0 = \text{mobility of elctron}$

$L_{eff}$  = channel length of transistor

$W_{\text{eff}} = \text{channel width of transistor}$

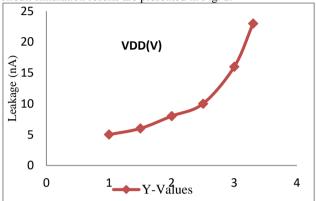

Equation (2) shows an exponential relation between I<sub>SN</sub> and V<sub>DD</sub>.

The current density dye to direct tunneling is given by (3) ... 3/2

$$J_{DT} = AE_{ox}^{2} (\frac{\phi_{ox}}{V_{ox}}) (\frac{2\phi_{ox}}{V_{ox}} - 1)e^{\frac{B[1 - (1 - \frac{Vox}{\phi_{ox}})]}{Eox}}$$

Where,  $A = \frac{q^{3}}{16\pi^{2}h\phi_{ox}}$  and  $B = \frac{4\sqrt{2m^{*}\phi_{ox}^{3/2}}}{3hq}$

$V_{ox}$ = voltage drop across the oxide Eox = ekectric field in the oxide Tox = oxide thicknss  $M^*$  = effective mass of an electron H= plank costant

# **3.Results and Discussion**

The proposed Low Power Ternary Content Addressable Memory circuit has been designed and implemented in  $0.35\mu m$  CMOS technology. The minimum supply voltage is 1.5 V and the maximum supply current is  $11.5\mu A$  at the maximum supply voltage of 2.5 V and the maximum temperature of operation is  $300^{0}$ K. The circuit simulation results are presented in Fig. 2.

Fig. 2 TCAM cell leakage for 0.18 µm technology

### 4. Conclusions

A TCAM circuit has been proposed and simulated results has been discussed. The simulation results show that the circuit is highly immune to supply and temperature variation. Simulation result shows upto 30% reduction in leakage and cell area over the conventional TCAM cell. This circuit can be used in network routers, search engine and other low-power applications.

#### Acknowledgement

This work has been performed on Mentor-Graphics Tools at VLSI Design Lab, Department of Electronics and Communication Engineering, Delhi Technical Campus, Greater Noida

#### References

[1] H Higuchi, S Tachibana, M Minami, T Nagano. A 5-mW, 10-ns cycle TLB using a high-performance CAM with low-power match detection circuits, IEICETransactions on Electronics, E79-C(6) 1996.

[2] M Sumita. A 800 MHz single cycle access 32 entry fully associative TLB with a 240ps access match circuit, Digest of Technical Papers of the Symposium on VLSICircuits, 2001, 231-232.

[3] P-F Lin, JB Kuo, A 1-V 128-kb four-way set-associative CMOS cache memory using wordline-oriented tag-compare WLOTC structure with the contentaddressable memory (CAM) 10-transistor tag cell, IEEE Journal of Solid-stateCircuits, 36(4), 2001,666-675.

[4] P-F Lin, JB Kuo, A 0.8-V 128-kb four-way set-associative twolevel CMOS cache memory using two-stage wordline/bitlineoriented tag-compare (WLOTC/BLOTC) scheme, IEEE Journal of Solid-state Circuits, 37(10), 2002, 1307-1317.

[5] JP Wade, CG Sodini. A ternary content-addressable search engine, IEEE Journal of Solid-state Circuits, 24(4), 1989.

[6] KJ Lin, CW Wu. A low-power CAM design for LZ data compression, IEEE Transactions on Computers, 49(10), 2000.

[7] T Ogura, M Nakanishi, T Baba, Y Nakabayshi, R Kasai, A 336kb content addressable memory for highly parallel image processing, Proceedings of the IEEECustom Integrated Circuits Conference (CICC), 1996, 273-276.

[8] F Yu, RH Katz, TV Lakshman. Gigabit rate packet patternmatching using TCAM, Proceedings of the IEEE International Conference on Network Protocols(ICNP'04), Berlin, Germany, 5.1.1-5.1.10, 2004.

[9] FYu, RH. Katz. Efficient multi match packet classification with TCAM, Proceedings of the IEEE Symposium on High Performance Interconnects (HOTI'04), Stanford, CA, 2.1.1-2.1.7, 2004

[10] RX Gu, MI Elmasry. Power dissipation analysis and optimization of deep submicron CMOS digital circuits, IEEE Journal of Solid-state Circuits, 31(5), 1996, 707-713.

[11] KF Schuegraf, C Hu. Hole injection SiO<sub>2</sub> breakdown model for very low voltage lifetime extrapolation," IEEE Transactions on Electron Devices, 41(5), 1994.

[12] The MOSIS Service. www.mosis.org

[13] Meribout M, Ogura T, Nakanishi M. On using the CAM concept for parametric curve extraction, IEEE Trans. Image Process, 9(12), 2000, 2126–2130.

[14]Mohan Nitin, Sachdev Manoj. Novel Ternary Storage Cells and Technique for Leakage Reduction in Ternary CAM, Proceeding of the IEEE International SOC Conference (SOCC), Austin, Texsas, Sep. 24-27, 2006.

[15]Pagiamtzis K, Sheikholeslami A. A low-power contentaddressable memory (CAM) using pipelined hierarchical search scheme, IEEE Journal of Solid-StateCircuits, 39(9),2004,1512– 1519.

[16]Pagiamtzis Kostas, Azizi Navid, Najm Farid N. A Soft-Error Tolerant Content-Addressable Memory (CAM) Using An Error-Correcting-Match Scheme, IEEE Custom Integrated Circuit Conference, 301-304, 2006.

[17]Pagiamtzis Kostas, Sheikholeslami Ali, Content-Addressable Memory (CAM) Circuits and Architectures: A Tutorial and Survey, IEEE Journal of solid state Circuits, 41(3), 2006.

[18]Rabaey JM. Digital Integrated Circuits: A Design Perspective, First Edition, Prentice-Hall Inc., Upper Saddle River, New Jersey, 1996.

[19]Ravikumar V.C., Mahapatra R.N., Bhuyan L.N., "EaseCAM: an energy and storage efficient TCAM-based router architecture for IP lookup," IEEE Transactions on Computers, vol. 54, no. 5, pp. 521-533, May 2005.

[20]Roth A, Foss D, McKenzie R, Perry D, Advanced ternary CAM circuits on 0.13μm logic process technology, Proceedings of the IEEE Custom IntegratedCircuits Conference (CICC), 465-468, 2004.

[21] Schultz KJ, Gulak PG. Architectures for large-capacity CAMs," Integration, VLSI J., 18(2–3), 1995, 151–171.

[22] Schultz KJ, Shafai F, Gibson GFR, Bluschke AG, Somppi DE. Fully parallel 25 MHz, 2.5-Mb CAM, in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, 332–333, 1998.

[23] Shafai Farhad, Schultz Kenneth J, Gibson GF Randall, Bluschke Armin G. Fully Parallel 30-MHz, 2.5-Mb CAM, IEEE Journal of Solid State Circuits, 33(11), 1998

[24] Stas S. Associative processing with CAMs, in Northcon/93 Conf. Record, 1993, 161–167.

[25] Tran H. Demonstration of 5T SRAM and 6T dual-port RAM cell arrays, Proceedings of the IEEE Symposium on VLSI Circuits, Honolulu, 13-15, 13-15 Jun. 1996.

[26]Vlasenko P, Perry D. Matchline sensing for content addressable memories, US Patent 6717876, Apr. 6, 2004.